글에 틀린 부분이 있을 수도 있습니다. 피드백은 언제나 환영입니다. 감사합니다.

1. 들어가며

이번 포스트에서는 de1 soc board에 대한 소개와 hps address space에 대해 적어보려고 한다.

2. DE1-SOC board 소개

Cyclone V는 두 개의 구역 - HPS(hard processor system)과 FPGA 두 개의 영역으로 구성된 soc이다. DE1-soc board는 이 Cyclone V soc 의 기능을 테스트하고 개발할 수 있는 하드웨어 플랫폼 중 하나이다. HPS는 dual ARM Cortex-A9 MPcore processors를 가진 microprocessor unit(MPU) subsystem, flash memory controller, SDRAM controller, L3 interconnect 등으로 이루어져 있고, FPGA는 FPGA fabric, control block(CB), phase-locked loops(PLLs) 등으로 이루어져 있다.

다음의 사진을 통해 HPS의 구성을 더 자세히 알 수 있다.

위의 사진을 보면 MPU subsystem, SDRAM controller, L3 interconnect 등이 있는 것을 볼 수 있다. MPU subsystem 안에는 dual ARM core가 있는데, core 당 하나씩의 mmu(memory management unit)을 갖고 있다.

Cyclone V에서는 HPS와 FPGA를 같이 사용할 때, bare-metal로 사용할 수도 있고 운영체제(Linux) 위에서 동작하게 할 수도 있는데, bare-metal로 동작할 땐 mmu를 거치지 않을 것이고, Linux 위에서 동작할 땐 mmu를 거치게 될 것이다. 암튼 이번 과제들은 다 리눅스 위에서 진행했으므로, 프로세스가 동작하기 위해서는 mmu를 거쳐서 논리주소가 물리주소로 변환되고, L2 캐시를 지나 SDRAM에 전달될 것이다.

한 가지 불분명한 것은, mmap 함수를 사용하면, 프로세스 주소공간에 physical address가 매핑되어 동작하는 것으로 알고 있는데, 이 경우에는 mmu를 거치지 않는 것인지, 아니면 다른 성격의 mmu를 거치는 것인지 잘 모르겠다. 이 부분에 대해서는 더 공부를 해봐야 할 것 같다.

2.1 Lightweight HPS to FPGA bridge

mmap 함수를 사용하면 위에서 설명했듯이, 프로세스의 주소공간에 physical address가 매핑된다. 우리는 이번에 HPS peripheral을 사용하지 않고 FPGA영역의 peripheral들을 사용했다. 위의 사진에 따르면 HPS와 FPGA의 peripheral을 연결하기 위해 3개의 bridge가 사용되는데, 우리는 FPGA영역의 peripheral에 접근하기 위해 Lightweight HPS to FPGA bridge를 사용했다. 이에 해당하는 address는 0xFF200000부터 2MB 크기이다.

2.2 memory(HPS)

HPS는 0x00000000에서 0x3FFFFFFF 주소공간에 매핑된 1GB DDR3 SDRAM을 갖고 있다. 이것은 보통 ARM processors에 의해 프로그램과 데이터의 저장소로 이용된다. 256M x 32-Bits 로 이루어져있으며, word, halfword, byte 단위로 접근 가능하다. 이외에도 HPS는 on-chip RAM, Boot ROM을 갖고 있다. on-chip RAM은 base address가 0xFFFF0000, 64KB size 이고, Boot ROM은 base address가 0xFFFD0000, 64KB size 이다.

2.3 parallel port

DE1-SoC Computer의 FPGA 안에는 ARM A9 processor와 I/O peripheral들 사이에 input, output, bidirectional transfer를 지원하는 parallel ports가 있다.

Figure 2에서 표현된 것처럼, 각각의 parallel port는 base address를 갖고 있고 최대 4개의 32-bit register를 포함한다. output capability를 가진 ports는 writable Data register를 갖고 있고, input capability를 가진 ports는 readable Data register를 갖고 있다. Bidirectional parallel ports 는 Direction register를 갖고 있다. 몇몇 parallel port들은 Base + 8, Base + C 위치에도 register를 갖고 있다.

1. RED LED Parallel Port

DE1-SoC 보드의 RED LED(LEDR) 은 ouput parallel port에 의해 구동된다. 해당 port의 주소는 0xFF200000이고, `10-bit Data register`를 포함하고 있다. 이 레지스터는 word 단위(32-bit) 접근에 의해 읽히거나 쓰여질 수 있다. 그리고 10번째 비트부터 31번째 비트까지는 무시된다.

2. 7-Segment Displays Parallel Port

DE1-SoC 보드에는 7-segment display가 6개 존재한다. 그리고 이를 위해 2개의 Data register가 있고 둘은 서로 연결되어 있다. 0xFF200020 에 있는 레지스터는 HEX3에서부터 HEX0까지 구동시키고, 0xFF200030에 있는 레지스터는 HEX5와 HEX4를 구동시킨다. 데이터는 word 단위 연산에 의해, 이 두 개의 레지스터에 쓰여질 수도 있고 읽혀질 수도 있다. 이 데이터는 Figure 4에 있는 bit의 위치에 따라 직접적으로 7-segment의 각각의 부분들을 조작한다. 7-segment의 6부터 0까지 각각의 위치들은 그림의 오른쪽에 나타나 있다.

3. Slider Switch Parallel Port

Slider Switch(SW)는 input parallel port와 연결되어 있다. Figure 5에 나와있는 것처럼, 이 포트는 10-bit read-only Data register로 이루어져 있다. 이 포트는 0xFF200040 에 매핑되어 있다.

4. Pushbutton Key Parallel Port

Pushbutton Key에 연결된 parallel port는 3개의 4-bit register로 이루어져 있다. 이 레지스터들의 base address는 0xFF200050이고 word 단위 연산에 의해 접근 가능하다. read-only Data register는 Pushbutton Key에 value 를 제공한다.

3. HPS address space

HPS는 0x00000000 에서 0xFFFFFFFF 까지 4GB의 주소 범위를 갖는 3개의 논리 주소 공간을 갖고있는데, 이를 이용하여 SDRAM, HPS의 peripheral, FPGA의 peripheral에 접근한다.

이 사진은 3개의 4GB 논리주소공간을 보여주고 있다. 여기서 MPU는 MPU subsystem을, L3는 L3 interconnect를, SDRAM은 SDRAM controller subsystem을 의미한다. 각각의 영역을 살펴보면 다음과 같다.

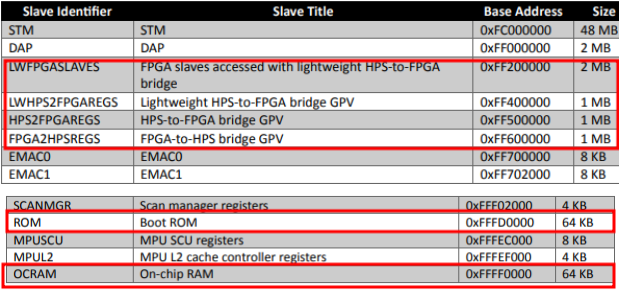

그리고 HPS peripheral의 address map은 다음과 같다.

2.1과 2.2에서 언급한 peripheral들의 address를 다시 한번 확인할 수 있다.

그리고 이 사진은 Figure1을 요약한 그림이다.

Figure7을 통해 MPU와 L3가 Lightweight FPGA slaves에 해당하는 address를 공유하는 것을 알 수 있다. 그래서 MP core에서 출발한 데이터와 명령어는 L2 cache → L3 interconnect → Lightweight HPS to FPGA bridge를 통해 전달되고 결국에 FPGA의 peripheral들을 제어할 수 있게 된다.

다음 포스터에서는 led를 제어하는 c프로그램을 예시로 사용하면서 mmap에 대해 더 자세히 작성해볼 예정이다.

[출처]

https://people.ece.cornell.edu/land/courses/ece5760/DE1_SOC/SoC-FPGA%20Design%20Guide_EPFL.pdf

https://www.researchgate.net/figure/Cyclone-V-SoC-architecture_fig1_325989906

'과제 및 프로젝트 > 임베디드 시스템 설계' 카테고리의 다른 글

| Polled I/O를 이용한 Calculator (0) | 2024.12.23 |

|---|---|

| Memory-Mapped IO in Linux-Based Systems(3) (0) | 2024.12.23 |

| Memory-Mapped IO in Linux-Based Systems(2) (0) | 2024.12.22 |